[Verilog Syntax] 02

주제: Declarations 1. Net(wire) 연결을 의미하며, 하나의 타입이다(그러므로 wire은 net이다). 이 자료형 자체는 일반적인 데이터 값을 저장할 수 없다.이 부분은 Vivado로 프로그래밍 하다보면 알 수 있는 데, 정말 그대로 어딘가로 연결되는 wire(선)이라고 생각하면 편하다. 종류: wire, supply0, supply1, tri, triand, trior, tri0, tri1, uwire, wand, wor Verilog에서는 일반적으로 wire을 많이 쓰며, 이 wire은 단일비트를 가진다. Declaration:wire Name1, Name2, Name3; // 단일 비트 net을 정의한다. 이 wire는 나중에 나올 module(모듈)의 I/O(Input/Outpu..

더보기

문제6. 탄도 위치 계산

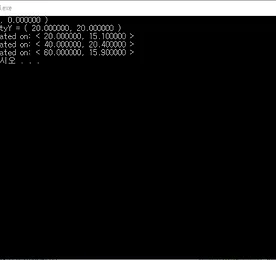

문제:어떠한 물체를 포물선 형태로 던진다고 하자. 1초, 2초, 3초 후 물체의 위치를 출력하여라. 단,1. 물체의 초기 위치는 (0,0)이다.2. x축 방향 초기 속도, y축 방향 초기 속도는 각 20m/s이다.3. 중력가속도 g는 9.8로 계산한다. 4. 시간에 따른 물체의 위치 (x, y)는 다음과 같다. 여기서 x_0, y_0는 물체의 초기 위치이며, v_x는 x축 방향의 초기 속도, v_y는 y축 방향의 초기속도, g는 중력가속도, t는 시간이다. 5. 중력 가속도, 초기 위치, 초기 속도를 상수로 정의하시오.6. for문을 사용하지 마시오. 화면: 해결방안: 5개의 float형 상수를 선언-정의한다.초기위치(startX, startY), 초기속도(velocityX, velocityY), 중력가..

더보기

문제6. 탄도 위치 계산

문제:어떠한 물체를 포물선 형태로 던진다고 하자. 1초, 2초, 3초 후 물체의 위치를 출력하여라. 단,1. 물체의 초기 위치는 (0,0)이다.2. x축 방향 초기 속도, y축 방향 초기 속도는 각 20m/s이다.3. 중력가속도 g는 9.8로 계산한다. 4. 시간에 따른 물체의 위치 (x, y)는 다음과 같다. 여기서 x_0, y_0는 물체의 초기 위치이며, v_x는 x축 방향의 초기 속도, v_y는 y축 방향의 초기속도, g는 중력가속도, t는 시간이다. 5. 중력 가속도, 초기 위치, 초기 속도를 상수로 정의하시오.6. for문을 사용하지 마시오. 화면: 해결방안: 5개의 float형 상수를 선언-정의한다.초기위치(startX, startY), 초기속도(velocityX, velocityY), 중력가..

더보기